CLCはMicrochip社のPICシリーズのMCUに組み込まれているソフトウェア的に構成を設定可能な組み合わせ・順序回路です。

- http://ww1.microchip.com/downloads/jp/DeviceDoc/41631A_JP.pdf

- 構成可能なロジックセルヒントとコツ

- http://ww1.microchip.com/downloads/jp/AppNotes/00002133A_JP.pdf

- CLC を使った PIC® MCU の機能拡張

- https://microchipdeveloper.com/8bit:clc

- CLC: Configurable Logic Cell

XENESISシリーズのハードウェアの中核技術

XENESISシリーズのSBC (Single Board Computer)の華は、言うまでもなくそれぞれのマイクロプロセッサですが、CLCはそれらを現代の技術も利用して再構成し楽しむための中核技術となっています。

XENESISシリーズのSBCの開発を行う際に、XENESISが成功する(まだしてないけど。。。)と確信した理由の1つがCLCの利用でした。(4-50年前のマイクロプロセッサを主題にしているSBCとしては反則技といえるかもしれませんね。)

- MPUやACIAのクロック生成にPICを使用すると、CLCがおまけで(むしろ主役だけど)付いてくる

- CLCでは、かなり複雑な組み合わせ回路と、順序回路を作成できることが確認できた

- CLCを8回路内蔵したPICが発表された

XENESISの回路設計を行う際に以下のような問題がありました。

- 少ないIC(SSI)では単純な最低限の構成の回路(制御回路とアドレスデコーダ)しか作れない。

- 少し気の利いた回路を作ろうとすると、IC(SSI)の種類と個数が増え、しかも未使用のゲートが残ったりして、スマート(おしゃれ?)じゃなくなる。

1つのICで柔軟性のある回路を構成しようとすると、GAL (Generic Array Logic)などを使うという手もありますが、順序回路が構成できなかったり、それとは別に、クロック生成用のPICなどを組み合わせる必要があります。

CLCを内蔵したPICを使用すれば、40年前だったらたくさんのICを使用するクロック生成器・制御回路・アドレスデコーダをたった一つのPICで構成できてしまいます。しかも、そのハードウェアの構成をソフトウェア的に、稼働時にさえ変更できるのです。

イヤーすごい時代になったものです。

CLCで構成したアドレスデコーダ

アドレスデコードにはアドレスバスの上位4ビットA15-A12を使用することで、4KBの領域を単位としてROM, RAM, IOの3種類の領域の選択信号を生成しています。アドレスデコード用の回路は、PIC18に内蔵されたCLC(Configurable Logic Cell)を利用して構成しています。

また、CLCはプログラムにより再構成できることを利用して、JP1のSEL2,SEL3を使用して、異なる用途に適合した3種類のアドレスマップに対応してアドレスデコードが行えるようにしています。

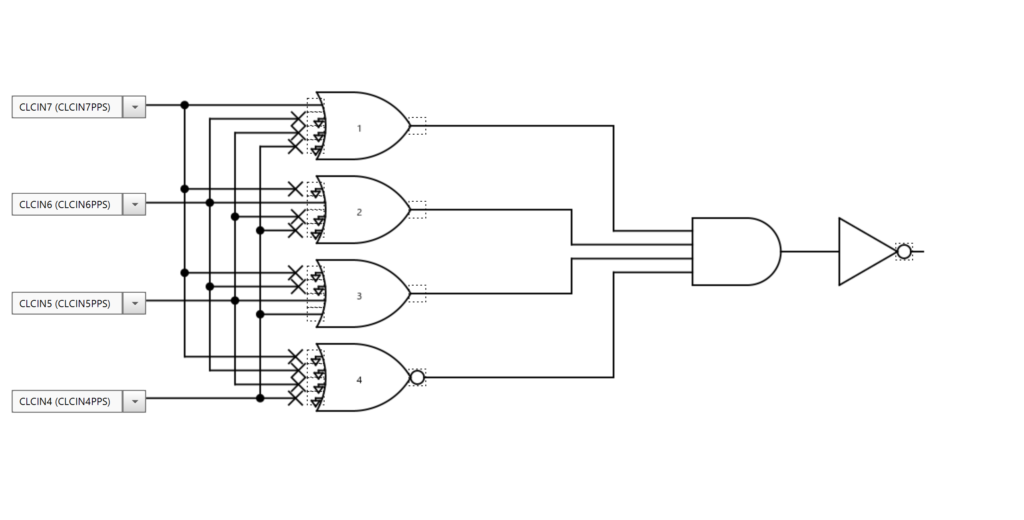

CLCを利用したROMのアドレスデコーダの例を「CLCによるROMのCS回路(12KB)」に示します。これは、ROMのチップセレクト信号を生成する回路で、入力端子のCLCIN7-CLCIN4にはそれぞれA15-A12が接続されています。

この回路の各ゲートの入出力端子の結線や論理の反転などはソフトウェアで制御することができ、「CLCによるROMのCS回路(12KB)」のように設定されると、ROMのうち最上位アドレスの12KBを使用するための回路になります。

また、JP1のSEL2,SEL3の設定を変えると、「CLCによるROMのCS回路(12KB)」の回路構成をソフトウェアで異なるものに書き換えて、ROMのうち最上位アドレスの4KBを使用するための回路に変更することができます。

CLCは「CLCによるROMのCS回路(12KB)」の構成も含め、フリップフロップを含む8回路から選択して、組み合わせ回路と順序回路構成することができます。

XENESISシリーズでは、このCLCを8組内蔵しているPIC18を使用して、高機能で柔軟性が高い制御回路を構成しています。

コンパクトな制御回路の実現

XENESISシリーズのシングルボードコンピュータでは、RAMとROMそれぞれが1チップのみで構成されていることと、CLCを内蔵するPIC18を活用することで、構成を変更可能なアドレスデコーダーを含む制御回路が驚くほどコンパクト(1個のICで)に構成されています。

1970年代に6800を使用したコンピュータを最初に作成した際には、XENESISシリーズと比べてRAMの容量が1/16の4KBであったにもかかわらず、メモリなども含めると50個以上のICを使用し、配線とはんだ付けに神経と労力を費やしていたことを思い出すと、隔世の感があります。

当時のシステムの使用IC数が多かった理由は以下のように考えられます。

- メモリの集積度が低く、例えば4KBのRAMを構成するだけでも32個のICを必要としたこと。

- バスにつなぐメモリの数が多いため、アドレスバスやデータバスにドライブ能力を向上させるためのドライバ・バッファを必ず挿入しなければならなかったこと。

- メモリICが多いと、アドレスデコード用の回路が大きくなりそのためのICが増えること。

- その他のこまごまとした回路を構成するために、機能の異なる複数のゲートICを(それぞれのパッケージ内の未使用ゲートが複数あっても)使わざるを得ないこと。

XENESISシリーズでは、(当時のシステムの観点で)大容量のROMとRAMを使用し、さらには、コンパクトかつ柔軟に回路を構成できるCLCを使うことにより、当時であれば多数のゲートを組み合わせて構成しなければならない組み合わせ回路を、コンパクトに構成できることになったことにより解消されています。